同步复位: always @(posedge clock) if (~reset)

异步复位: always @(posedge clock or negedge reset) if (~reset)

同步复位优点:

1、有利于仿真器仿真。

2、可使系统成为100%同步时序电路,有利于时序分析,可综合出的最高工作频率数值较高。

3、复位在时钟边沿到来时有效,可滤除高于时钟频率的毛刺。

同步复位缺点:

1、复位信号有效时间长度必须大于时钟周期,才能真正被系统识别并完成复位,必须考虑时钟偏移、组合路径延迟、复位延时。

2、必须有时钟才能完成复位。

异步复位优点:

1、复位简洁,不受时钟影响。

异步复位缺点:

1、受复位信号与时钟信号不相关影响,容易产生亚稳态,造成复位紊乱。

2、易受毛刺影响触发误复位。

3、复位信号和时钟信号异步不利于仿真和综合。

质疑:

1、同步复位真的不受复位信号与时钟信号不相关影响,真的可以“同步”复位吗?

复位信号和其它信号一样,需要满足建立时间和保持时间,所以同步复位用到的复位信号和下面要提到的异步复位同步释放一样,必须处理成和时钟同步,否则一样出现亚稳态,造成复位紊乱。

2、同步复位能否完全避免复位信号毛刺影响?

在采样时钟沿时的复位信号毛刺也可能造成复位错误,但比异步复位要好很多,异步复位在时钟全周期都受复位信号毛刺影响。

3、陷阱!

引入时钟门控后,同步复位会产生无法绝对避免的隐患。上电时,更严重的是子模块复位时忘记启动时钟,会造成系统状态紊乱。特别是在对电路做细粒度时钟门控时,非常容易忽略细微的条件。

可否结合同步复位和异步复位的优点?于是提出了异步复位,同步释放。

异步复位,同步释放:

1、复位信号产生立即复位。

2、复位状态解除在时钟沿完成。

实现途径:捕获复位信号释放状态,在时钟沿输出使用。

reg d1;

reg d2;

always @(posedge clock or !reset) begin

if (!reset) begin

d1 <= 1’b0;

d2 <= 1’b0;

else begin

d1 <= 1’b1;

d2 <= d1;

end

end

复位信号reset在寄存器内部和d相与,如果其上升沿刚好和时钟上升沿接近,则会在d1生成不定态,或为0,或为1。

d1为1,则持续为1,d2在下一个时钟为1,复位解除;

d1为0,则d2也保持0,下一周期d1为1,d2在下下周期为1,复位解除。

d2会不会生成不定态?不会。因为其输入被d1锁定为0,变为1时至少在复位信号升高一个时钟周期之后,屏蔽掉复位信号不定态(复位信号和0相与)。

上述电路实现两种功能:

1、将复位信号锁定在时钟沿。

2、滤除亚稳态。

存在问题:

1、仍然在全部时钟周期存在受复位信号毛刺影响的隐患,不能像同步复位一样将时钟沿外的毛刺天然滤除。

毛刺可否在其它维度受控?

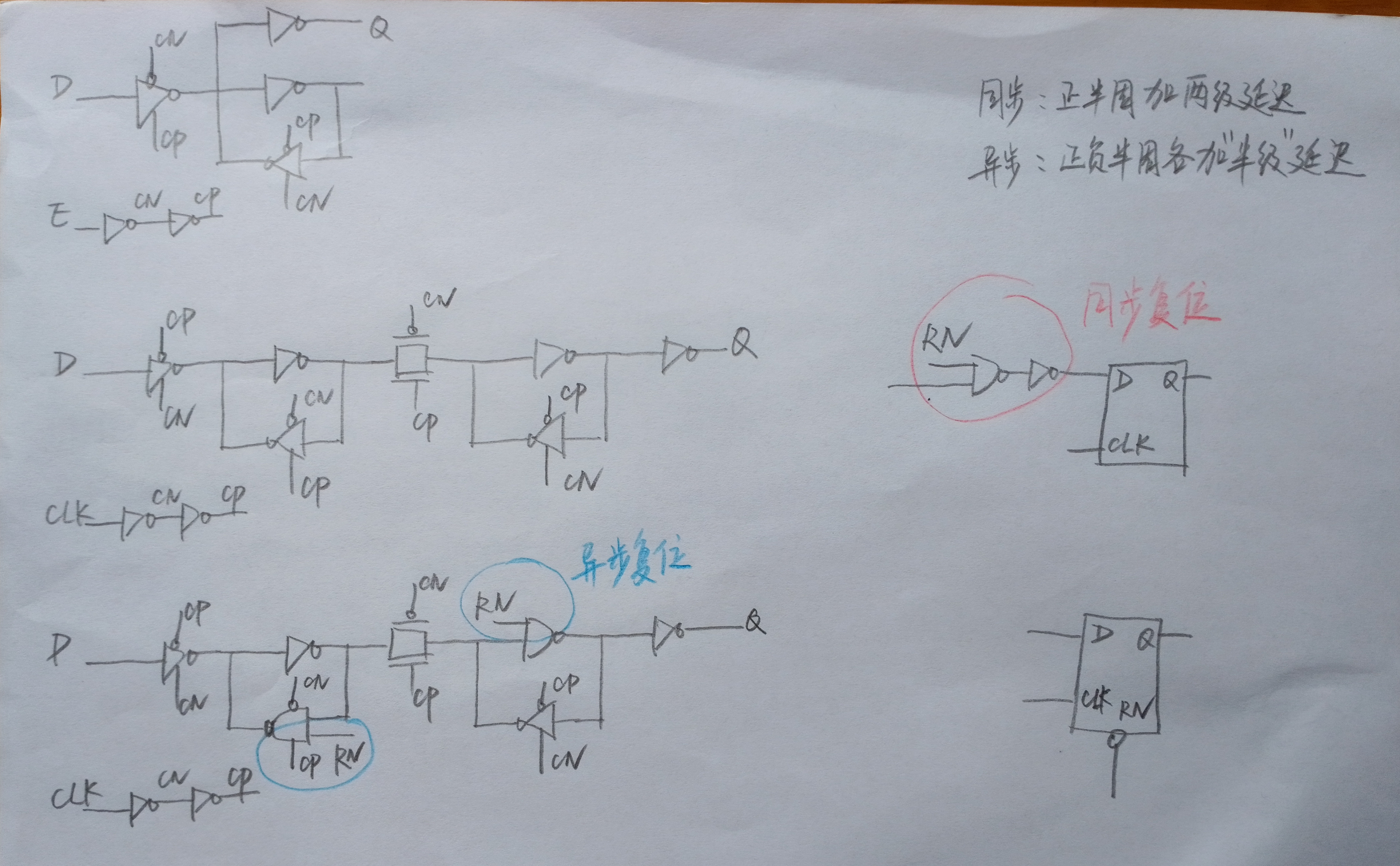

同步复位物理实现:

正半周数据通路将一个反向器改为与非门,正半周引入“半级”延迟。

(单元库无同步复位寄存器时时钟正半周数据通路插入与门,引入两级延迟,以下不予讨论)

异步复位物理实现:

正负半周数据通路各将一个反向器改为与非门,正负半周分别引入“半级”延迟。

◎ 电路图

◎ 电路图

小结:

1、同步复位单元面积和功耗都小于异步复位。

2、同步复位抗干扰能力强于异步复位。

异步复位抗干扰能力差源于复位信号参与数据保持阶段运算(对上升沿复位而言是时钟负半周),该阶段捕获的错误将在下个时钟沿向后传递。所以,上述异步复位全周期受复位信号毛刺影响的表述是不准确的(之所以不说是错误的,是因为可能一个电路中既存在上升沿采样、又存在下降沿采样)。

如果只将寄存器采样通路中的一个反向器替换为与非门,保持通路不变,则异步复位退化为同步复位。

3、同步复位存在门控陷阱。

引入时钟门控后可能产生复位时忘记开启时钟导致未实现复位的情况。